UNIVERSITY OF CALIFORNIA SANTA CRUZ

## **Objective-Based Routing For Physical Design-For-Test**

A dissertation submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

Computer Engineering

by

Richard McGowen

June 1995

The dissertation of Richard McGowen is approved:

F. Joel Ferguson

John M. Acken

Tracy Larrabee

Dean of Graduate Studies and Research

Copyright © by Richard McGowen 1995

## Contents

| Al         | Abstract         |          |                                             |    |  |

|------------|------------------|----------|---------------------------------------------|----|--|

| A          | A cknowledgments |          |                                             |    |  |

| 1.         | Intr             | roducti  | ion                                         | 1  |  |

| <b>2</b> . | Phy              | vsical I | Design-For-Test Overview                    | 3  |  |

|            | 2.1              | Cell N   | Iodifications                               | 3  |  |

|            |                  | 2.1.1    | Targeting Stuck-Open Faults                 | 3  |  |

|            |                  | 2.1.2    | Local Transformations                       | 4  |  |

|            | 2.2              | Routin   | ng Modifications                            | 6  |  |

|            |                  | 2.2.1    | Routing and Placement Suggestions           | 6  |  |

|            |                  | 2.2.2    | Classifying Faults for P-DFT                | 7  |  |

|            |                  | 2.2.3    | P-DFT Based Upon Testability and Likelihood | 8  |  |

|            |                  | 2.2.4    | Targeting Fanout-Free Regions               | 8  |  |

|            | 2.3              | Induct   | tive Fault Analysis                         | 8  |  |

| 3.         | Cha              | annel F  | Routing Overview                            | 10 |  |

|            | 3.1              | Chann    | nel Routing in General                      | 10 |  |

|            |                  | 3.1.1    | Terminology                                 | 10 |  |

|            |                  | 3.1.2    | Distinctions Between Channel Routers        | 11 |  |

|            |                  | 3.1.3    | Comparing Channel Routers                   | 14 |  |

|            | 3.2              | Gener    | al Purpose Channel Routers                  | 18 |  |

|            |                  | 3.2.1    | Left-Edge Algorithm                         | 18 |  |

|            |                  | 3.2.2    | "Greedy" Channel Router                     | 20 |  |

|            |                  | 3.2.3    | Yoshimura and Kuh                           | 21 |  |

|    |                                     | 3.2.4                            | Yet Another Channel Router 2                 | 22 |  |  |  |  |

|----|-------------------------------------|----------------------------------|----------------------------------------------|----|--|--|--|--|

|    |                                     | 3.2.5                            | Glitter                                      | 24 |  |  |  |  |

|    | 3.3 Goal Driven Channel Routers     |                                  |                                              | 26 |  |  |  |  |

|    |                                     | 3.3.1                            | Channel Routing With Analog Considerations   | 27 |  |  |  |  |

|    |                                     | 3.3.2                            | Channel Routing for the Improvement of Yield | 30 |  |  |  |  |

| 4. | ΑT                                  | A Testability Enhancing Router 3 |                                              |    |  |  |  |  |

|    | 4.1                                 | MCR                              |                                              | 33 |  |  |  |  |

|    |                                     | 4.1.1                            | Efficiency of Track Assignment               | 38 |  |  |  |  |

|    | 4.2                                 | Wire S                           | Separation                                   | 39 |  |  |  |  |

|    |                                     | 4.2.1                            | Horizontal Wires                             | 40 |  |  |  |  |

|    |                                     | 4.2.2                            | Vertical Wires                               | 41 |  |  |  |  |

|    | 4.3                                 | Experi                           | imental Procedure                            | 44 |  |  |  |  |

|    | 4.4                                 | Experi                           | iments and Results                           | 45 |  |  |  |  |

|    |                                     | 4.4.1                            | Penalizing Nets 500 Weighting Units          | 45 |  |  |  |  |

|    |                                     | 4.4.2                            | Improvement By Looking Ahead                 | 47 |  |  |  |  |

|    |                                     | 4.4.3                            | Variations in Penalty Weight                 | 51 |  |  |  |  |

|    |                                     | 4.4.4                            | Vertical Adjacency                           | 56 |  |  |  |  |

|    |                                     | 4.4.5                            | Combined Reductions                          | 60 |  |  |  |  |

|    | 4.5                                 | Conclu                           | isions                                       | 61 |  |  |  |  |

| 5. | Reductions in Undetectable Shorts 6 |                                  |                                              |    |  |  |  |  |

|    | 5.1                                 | Static-                          | Voltage Testing                              | 62 |  |  |  |  |

|    |                                     | 5.1.1                            | Motivation                                   | 62 |  |  |  |  |

|    |                                     | 5.1.2                            | Methodology                                  | 64 |  |  |  |  |

|    |                                     | 5.1.3                            | Undetectable Shorts                          | 64 |  |  |  |  |

|    |                                     | 5.1.4                            | Locality of Undetectability                  | 68 |  |  |  |  |

|    |                                     | 5.1.5                            | Locality as an Objective                     | 70 |  |  |  |  |

|    |                                                           | 5.1.6                        | Results                                             | . 71                 |

|----|-----------------------------------------------------------|------------------------------|-----------------------------------------------------|----------------------|

|    |                                                           | 5.1.7                        | Conclusions                                         | . 75                 |

|    | 5.2                                                       | Segme                        | entation                                            | . 75                 |

|    |                                                           | 5.2.1                        | Motivation                                          | . 75                 |

|    |                                                           | 5.2.2                        | Experimental Procedure                              | . 76                 |

|    |                                                           | 5.2.3                        | Results                                             | . 76                 |

|    |                                                           | 5.2.4                        | Conclusions                                         | . 77                 |

|    |                                                           |                              |                                                     |                      |

| 6. | App                                                       | plicatio                     | ons to Routing in General                           | 78                   |

| 6. | <b>Арј</b><br>6.1                                         |                              | ons to Routing in General<br>ve Importance of Goals |                      |

| 6. |                                                           | Relati                       |                                                     | . 78                 |

| 6. | 6.1                                                       | Relati<br>Genera             | ve Importance of Goals                              | . 78<br>. 79         |

| 6. | 6.1<br>6.2                                                | Relati<br>Genera<br>Illustra | ve Importance of Goals                              | . 78<br>. 79<br>. 80 |

|    | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul> | Relati<br>Genera<br>Illustra | ve Importance of Goals                              | . 78<br>. 79<br>. 80 |

# List of Figures

| 2.1  | Koeppe's second suggested modification                                              | 4  |

|------|-------------------------------------------------------------------------------------|----|

| 2.2  | Levitt's and Abraham's transform 1                                                  | 5  |

| 2.3  | Levitt's and Abraham's transform 2                                                  | 5  |

| 2.4  | Levitt's and Abraham's transform 3                                                  | 5  |

| 3.1  | Basic channel terminology                                                           | 10 |

| 3.2  | Routing grid                                                                        | 11 |

| 3.3  | Channel with 4 tracks                                                               | 12 |

| 3.4  | Channel with 16 columns                                                             | 12 |

| 3.5  | Examples of density                                                                 | 15 |

| 3.6  | Example VCV                                                                         | 16 |

| 3.7  | Vertical constraint graph                                                           | 17 |

| 3.8  | Horizontal net segments represented as intervals                                    | 18 |

| 3.9  | Sample net assignment                                                               | 19 |

| 3.10 | Examples of maze1                                                                   | 23 |

| 3.11 | Example of maze2                                                                    | 23 |

| 3.12 | Example of maze3                                                                    | 24 |

| 3.13 | Undirected edge directed from C to B                                                | 25 |

| 3.14 | Undirected edge directed from B to C                                                | 26 |

| 4.1  | Placing nets in tracks                                                              | 33 |

| 4.2  | Illustration of net weights when placing nets in the topmost track. $\ldots$ .      | 34 |

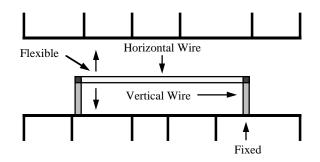

| 4.3  | Illustrations of horizontal/vertical segments and their flexibility in being moved. | 39 |

| 4.4  | Example of three types of potentially undetectable shorts between vertical          |    |

|      | wires                                                                               | 41 |

| 4.5  | Example of how to separate Nets 1 and 2                                             | 42 |

| 4.6  | Example of how to increase spacing between Nets 5 and 6                                    | 42 |

|------|--------------------------------------------------------------------------------------------|----|

| 4.7  | What channel looks like after removing unnecessary vias                                    | 43 |

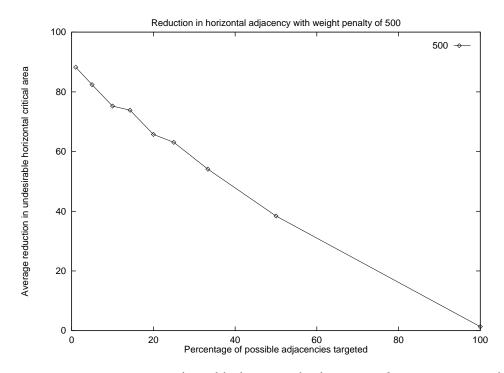

| 4.8  | Reduction in undesirable horizontal adjacencies for a weight penalty of 500.               | 45 |

| 4.9  | Illustration of final track problem.                                                       | 46 |

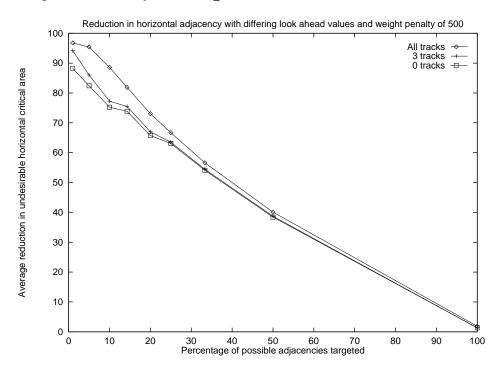

| 4.10 | Reduction in undesirable horizontal adjacencies when look-ahead encourage-                 |    |

|      | ment is used.                                                                              | 47 |

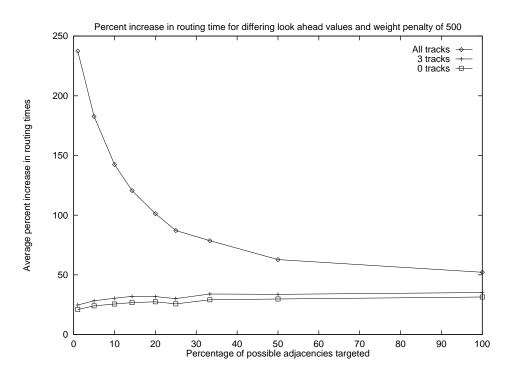

| 4.11 | Increase in routing time when look-ahead encouragement is used                             | 49 |

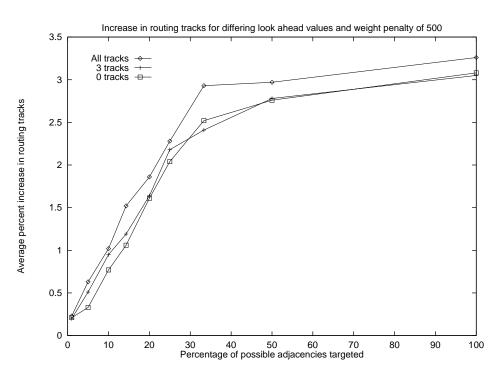

| 4.12 | Increase in routing tracks when look-ahead encouragement is used                           | 50 |

| 4.13 | Decrease in undesirable horizontal adjacency with full look-ahead and differ-              |    |

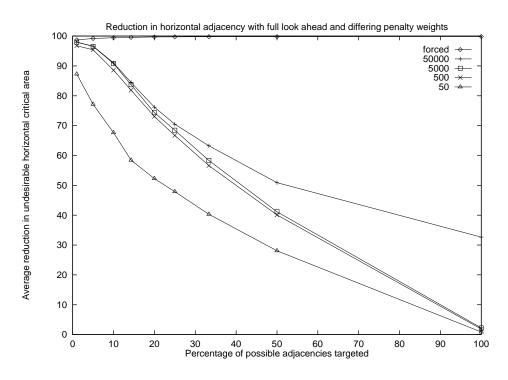

|      | ing weights                                                                                | 53 |

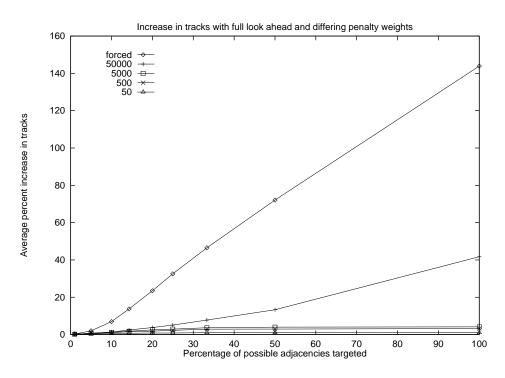

| 4.14 | Increase in routing tracks with full look-ahead and differing penalty weights.             | 54 |

| 4.15 | Increase in run time with full look-ahead and varying penalty weights                      | 55 |

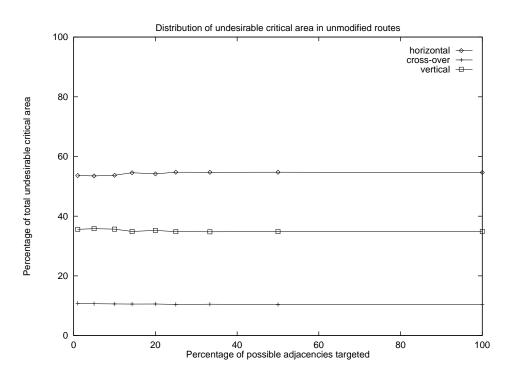

| 4.16 | Distribution of undesirable adjacencies for differing target percentages                   | 56 |

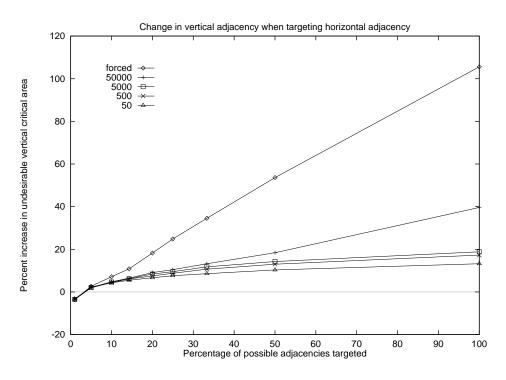

| 4.17 | Changes in undesirable vertical adjacencies when targeting undesirable hor-                |    |

|      | izontal adjacencies with differing weights and full look-ahead. $\ldots$ $\ldots$ $\ldots$ | 57 |

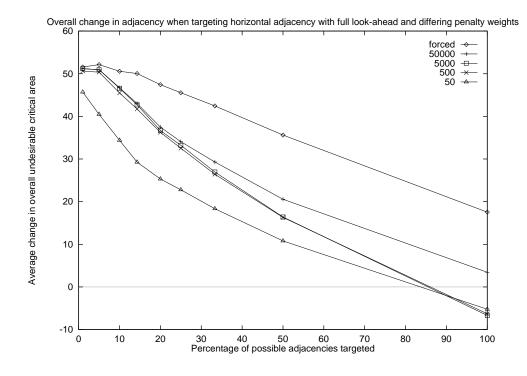

| 4.18 | Overall decrease in undesirable adjacency when all types of adjacency are                  |    |

|      | considered with differing penalty weights and full look-ahead. $\ldots$                    | 58 |

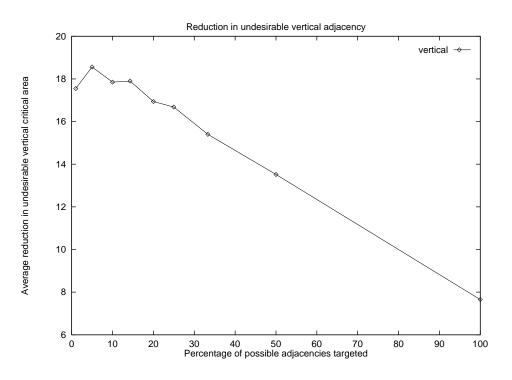

| 4.19 | Decrease in vertical adjacency.                                                            | 59 |

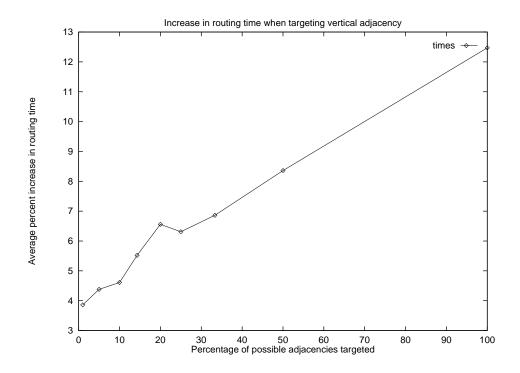

| 4.20 | Increase in routing time when targeting vertical adjacencies                               | 59 |

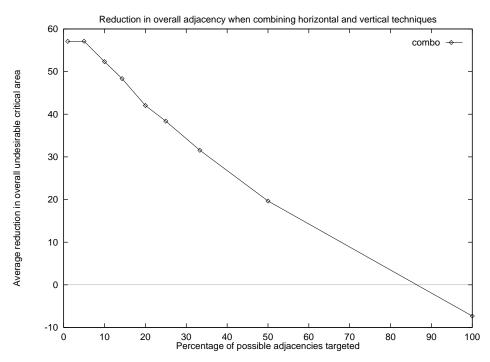

| 4.21 | Overall decrease in undesirable adjacency when horizontal and vertical tech-               |    |

|      | niques are combined. The weight penalty is set to 5000 and a full look-ahead               |    |

|      | is used                                                                                    | 60 |

| 5.1  | Example of how unintentional redundancy may be introduced                                  | 65 |

| 5.2  | Example of redundant circuitry taken from the 1908                                         | 65 |

| 5.3  | Single gate that performs the same function as the logic in Figure 2. $\ldots$             | 66 |

| 5.4  | Example taken from 2670 that shows two types of masking that can occur.                    | 66 |

| 5.5  | Additional example of masking through function equivalence                                 | 67 |

| 5.6 | Example of a non-excitable LD short.   | 69 |

|-----|----------------------------------------|----|

| 5.7 | Example of a non-propagatable LD short | 69 |

#### **Objective-Based Routing For Physical Design-For-Test**

Richard McGowen

#### ABSTRACT

This dissertation describes how objective-based routing can be used to create circuits that are more testable. It presents techniques that allow the importance of routing time, routing area, and testing difficulty to be weighed against one another. These techniques vary the strength of an objective function to take the relative importance of differing goals into account. These techniques achieve significant improvements in testability with minimal time and area penalties. This dissertation presents methods for using the routing techniques to efficiently improve the testability of circuits under the static-voltage and pseudo-exhaustive testing methodologies and gives results for sample circuits. It discusses the relevancy of varying strength objectives to routing in general.

**Keywords:** Routing, Channel Routing, CAD, VLSI Layout, DFT, P-DFT, Testability, Design For Test, Goal-Oriented Routing

## Acknowledgments

I would like to thank Sequoia Semiconductor and Silicon Engineering for providing the motivation and funding for my original implementation of Yoeli's router. I would like to thank the NSF and the SRC for their support of my later work.

I would like to thank Dr. F. Joel Ferguson for his support. His help and insights were much appreciated. (He also plays a pretty mean game of 1830.)

I would like to thank John M. Acken and Tracy Larrabee for agreeing to be on my committee and for their useful suggestions. I would like to thank Jon Udell for providing a copy of his segmentation software.

Finally, I would like to thank my wife, Janet McGowen, for encouraging me to finish writing my dissertation and for her general support.

## 1. Introduction

During the fabrication of an integrated circuit, errors may occur that cause two wires to be shorted together. Unintentional shorts are undesirable as they may cause a circuit to fail or may decrease its long-term reliability. In order to detect such shorts, the circuit must be tested. However, some shorts are more difficult to detect than others. Some may be undetectable. Increasing quality requirements drive the need for Physical Design-For-Testability. The goal of this research is to define and demonstrate how an objective-based channel router improves testability.

To ease the testing problem and increase the likelihood of shorts being detected, the probability of an undetectable or hard-to-test short occurring should be reduced. This can be accomplished by generating circuit layouts that have increased spacing, or additional wires, between wire pairs that could potentially cause undetectable shorts. When improving testability, care must be taken to ensure that this is not detrimental to the achievement of other, more important, goals. Since the relative importance of goals varies from design to design, it is important that the router be able to vary the strength with which it increases testability. The importance of a goal may range from that of an *objective*, a goal that should be met, to a constraint, a goal that must be met. Although increased testability is important, it is not necessary and can be considered an objective. To allow trade-offs to be made with other goals, such as routing time or routing area, the router should be capable of varying the relative strength with which it increases testability. This can be done by using a carefully designed weighting scheme.

This dissertation describes a channel router that makes use of the above ideas to generate more testable circuits. First, previous work on improving the testability of circuits through layout modification is presented. Next, an overview of channel routing and goal-oriented routing is given. The development of a channel router that improves testability is then described and its performance measured. It is then shown how the routing techniques can be used to generate more testable circuits. The applicability of the underlying ideas to routing in general is then discussed. Finally, areas of future work and conclusions are presented.

### 2. Physical Design-For-Test Overview

Physical Design-For-Test (P-DFT) is the process of changing the layout of a circuit to make it more testable. It is a subset of Physical Design-For-Manufacturability (P-DFM), the process of modifying the layout of a circuit to produce and ship a larger number of good die. Some of the work presented in this chapter provides both P-DFT and P-DFM techniques. The P-DFM techniques are included because they also improve the testability by relaxing the importance of testing for specific faults, even though their primary focus is improving other manufacturability aspects, such as reliability.

#### 2.1 Cell Modifications

One way in which the testability of circuits has been improved has been to change the layout of cells so that the cells themselves are more testable. One reason for doing this is to take advantage of the reuse of cells within a circuit and across many designs. By investing effort in cell design, a large improvement in testability can be gained since the cells will be used many times.

#### 2.1.1 Targeting Stuck-Open Faults

In 1987, Koeppe provided layout rules for decreasing the likelihood of occurrence of hard-to-test stuck-open faults and for improving their testability should they occur [Koe87]. Stuck-open faults present particular problems when they occur in parallel paths in CMOS gates as they can introduce state into the circuit and require a sequence of patterns to test a single fault[Wad78]. To ease this problem, Koeppe suggested three modifications that can be made to cells during the layout process.

The first modification targets opens in paths to power or ground. Parallel paths are replaced with a ring-shaped LOCOS structure. Moving the parallel paths into the diffusion layer provides two advantages. The diffusion layer is less likely to experience a break fault

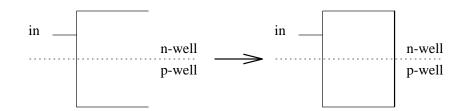

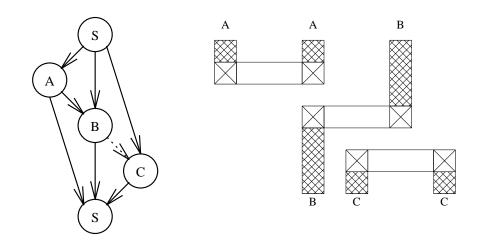

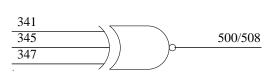

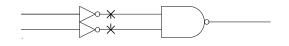

Figure 2.1: Koeppe's second suggested modification.

(DFM), A break in the metal layer or a contact will now disconnect the entire parallel network; thus the fault can usually be detected with a simple stuck-at test (DFT).

The second modification targets the susceptibility of gate inputs to opens. It applies to cells created with a vertical-well design style which are defined by Koeppe as one in which "the n-wells and p-wells are arranged in parallel with the direction of the data flow". For these cells, he suggests closing metal input line branches to form a single loop as shown in Figure 2.1. Doing this provides redundancy that can overcome a single break in the input line.

The third modification targets the testability of gate input to opens for the horizontalwell design style. In this case, Koeppe suggests that input lines be branchless and connect to gates in parallel paths before gates in serial paths. By wiring inputs up in this manner, testing is eased since any break in an input line will disconnect the serial path transistor(s), which, like the first modification, causes an easily detectable stuck-open fault. The fault is easily detectable since either the pull-up or pull-down path (whichever is serial) will be totally disconnected and once a parallel path has precharged the output, the fault will behave as a stuck-at fault.

#### 2.1.2 Local Transformations

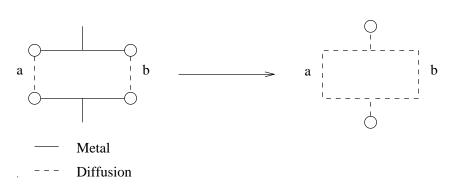

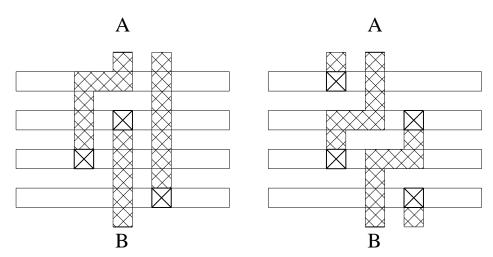

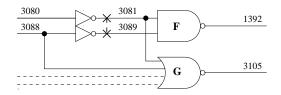

Levitt and Abraham also considered the problem of enhancing testability through the modification of cell layouts [LA90]. They devised a method whereby local transformations can be performed on an extended switch-graph representation of a circuit to increase its testability. The first transformation they proposed, shown in Figure 2.2, is equivalent to

Figure 2.2: Levitt's and Abraham's transform 1.

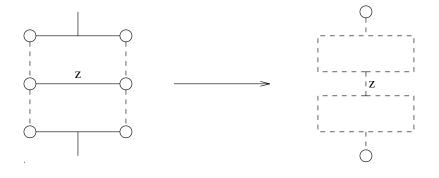

Figure 2.3: Levitt's and Abraham's transform 2.

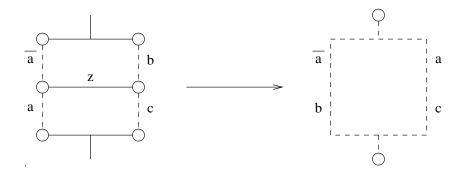

Figure 2.4: Levitt's and Abraham's transform 3.

Koeppe's LOCOS modification. The second transformation, shown in Figure 2.3, combines the first transformation with an additional replacement of any intermediate metal line with diffusion. In addition to having the benefits of the first transformation, this transformation increases reliability by removing a metal line and a couple of contacts, all of which are more likely to break than diffusion. This in turn leads to easier testing, as one can, for practical purposes, now ignore a break in line z. Before the transformation, a break in z would be relatively difficult to detect since come complete single-stuck-at test sets will not detect this fault. After the transformation, a break in z causes a stuck-at fault by disconnecting the circuit output from the power rail. The third transformation, shown in Figure 2.4, is similar to the second except that now line z is removed altogether. This is a specialized case as it requires a variable to be present in both parallel networks, being complemented in one and uncomplemented in the other.

#### 2.2 Routing Modifications

Another means of improving the testability of circuits is to modify the routing. In general, this is accomplished by separating lines to reduce the likelihood of undesirable shorts occuring. Several papers advocate improving testability through routing [Ack88, TTA+91, SCS+92, FKM92, Fer93], but little actual work has been done [MF94b, MF94a].

#### 2.2.1 Routing and Placement Suggestions

In his Ph.D. work, John M. Acken discussed reducing the likelihood of occurrence of shorts and increasing the testability of the shorts that do occur with routing [Ack88]. He suggests that outputs of multi-input gates should be adjacent to as few other lines as possible. The more inputs a gate has, the harder it is to control. If a short occurs between two lines that are difficult to set to different values, the short may be hard to detect. Acken also suggests that segment crossing shorts be avoided. Under the pseudo-exhaustive testing techniques, a circuit is divided into segments and each segment is exhaustively tested. If a short occurs between two lines in the same segment, pseudo-exhaustive testing is guaranteed to detect the short if it can be detected with a single input pattern. If a short occurs between two lines in different segments, detection is not guaranteed.

Other routing suggestions include giving preference of use to routing layers that are less susceptible to shorts and giving preference of avoidance to either adjacencies or crossovers, depending on which is more susceptible to shorts. Since the routing is in large part determined by the placement, he recommended that testability should be improved during cell placement and discussed how to do this for circuits tested with the pseudo-exhaustive testing methodology. By modifying the placement of cells so that cells in the same segment are grouped together within the layout, testability can be enhanced because adjacent wires are now more likely to be in the same segment.

#### 2.2.2 Classifying Faults for P-DFT

Teixeira *et al.* suggested dividing realistic faults into fault classes based upon their resistance to stuck-at test sets [TTA<sup>+</sup>91]. The different fault classes can then be used to focus DFT attention where it is most needed, namely on fault classes that are hard to detect and contain large numbers of faults. Once an important fault class has been identified, modifications can be guided by tracing the fault class back to its Physical Failure Mode(s) (PFM). An understanding of the PFM can be used to guide the derivation of DFT rules for the fault class.

The work of Teixeira *et al.* was further developed in a later paper [SCS<sup>+</sup>92]. In this paper, Saraiva *et al.* increased the granularity of the bridging fault category and gave DFT rules. A metric, called *Rule Violation Severity* (RVS) was given to help guide the application of DFT rules. The RVS metric helps formalize the importance of avoiding a particular fault-type based on how often it occurs and how likely it is to be detected. They stressed the importance of judicious application of DFT rules to avoid large area penalties. They gave the following DFT strategies:

- Cell versioning: Identify difficult-to-test areas and use test-based layouts of cells, rather than the performance-based layouts of cells, in these areas.

- Testability constrained routing: Identify difficult-to-test routing areas and increase the distance between lines in these areas.

- Selective decompaction: Identify difficult-to-test areas where routing lines or cells are close together and spread them out into sparse neighboring areas.

#### 2.2.3 P-DFT Based Upon Testability and Likelihood

Along similar lines, Khare and Maly suggested that routing and placement can improve testability by taking a testing based objective function into account [FKM92]. They suggest using a measure of overall testability to choose between different solutions. They recommend a testability measure based on probability of detection and probability of occurrence. For probability of detection, they suggest using the Sandia Controllability and Observability Analysis Program (SCOAP) measures. For probability of occurrence, they suggest using critical area measures for each failure mode. By then weighting each fault's probability of detection by its probability of occurrence, and summing these numbers for all the faults in the circuit, they feel that a measure of circuit testability can be achieved. One can then use this measure to compare the testability of different solutions and, by using an iterative process, maximize the testability.

#### 2.2.4 Targeting Fanout-Free Regions

In 1993 Ferguson said that routing could be used to avoid placing lines adjacent to each other if a short between them would cause feedback [Fer93]. Since separating all such lines is potentially too expensive, he said that the criteria could be relaxed. A router could target only lines where there is no fanout in the region between the two lines and the line closer to the output is more strongly driven.

#### 2.3 Inductive Fault Analysis

In order to develop P-DFT techniques and to measure their improvements, it is important to know which faults can actually occur in a given layout. Inductive Fault Analysis (IFA) techniques provide a means of determining this [MFS84, Fer87, FS88]. Carafe is an example of an IFA tool [JF93].

Carafe is a realistic fault extractor that, given a circuit's layout, process technology information, and fabrication defect characteristics, calculates which shorts and opens can occur if a spot defect modifies a circuit during the manufacturing process. Carafe reports which faults can occur and reports *critical area* totals for each fault. The critical area for a given fault is the total amount of area in which the center of a spot defect could land and cause the fault to occur. Critical area totals provide a means of measuring the likelihood of a given short occurring and thus how important it is that it be covered. Critical area coverage relates more closely to quality levels than fault coverage. Critical area totals also allow the impact of changes that reduce, but do not eliminate, the likelihood of a short occurring to be measured.

## 3. Channel Routing Overview

This chapter presents a sampling of previous work on channel routing and discusses previous work on goal-driven channel routing. This chapter provides an understanding of general and goal-oriented channel routing so that the work presented later for improving testability may be put in perspective.

#### 3.1 Channel Routing in General

Channel routing was developed as an efficient, automated method of generating wiring for two-layer printed circuit boards [HS71]. It has since been adapted to efficiently generate the interconnect for integrated circuits. The strength of channel routing is that it constrains and divides the wiring problem, making the overall interconnect generation problem less difficult.

#### 3.1.1 Terminology

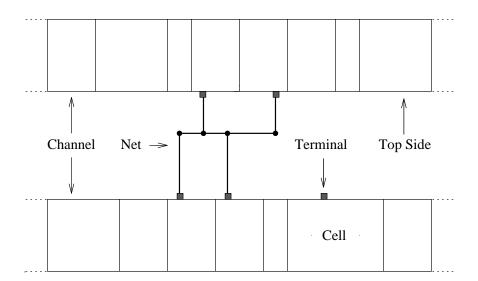

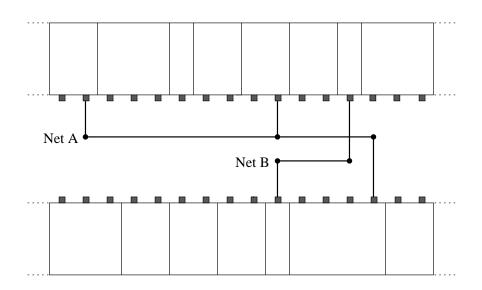

Figure 3.1: Basic channel terminology

Some definitions of channel routing terms follow. Refer to Figure 3.1 for examples. The *channel* is the rectangular region between two parallel rows of cells in which channel routing

is performed. Since it is customary to place cells into horizontal rows, the top side of the channel is the side closest to the upper row of cells.

A *terminal* is a point on a channel edge to which a connection must be made. Terminals represent the inputs and outputs of cells along the channel and connections to other channels above and below the channel being considered. In channel routing, only the locations of terminals along the top and bottom sides are fixed. If the locations of the side terminals are fixed, the routing problem is not considered channel routing, but rather switch-box routing.

A *net* represents an electrical connection between two or more terminals. Each net becomes a set of connected wire segments when the chip is fabricated.

A *wiring model* specifies how the wire segments will be physically represented. It specifies how many layers are available for wiring, the directions in which wires may run, and how they may overlap.

Using the above terms, the channel routing problem can be defined as: Given a channel, a list of nets, and a wiring model, generate an efficient physical representation of the nets that obeys the rules of the wiring model.

3.1.2 Distinctions Between Channel Routers

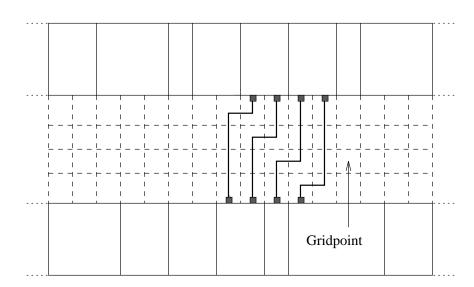

Figure 3.2: Routing grid

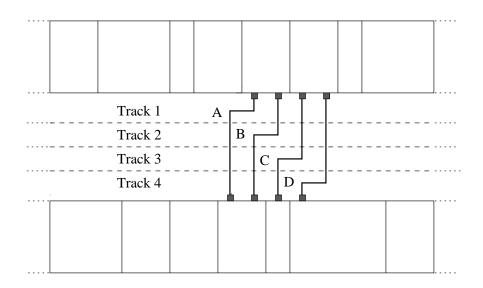

Figure 3.3: Channel with 4 tracks

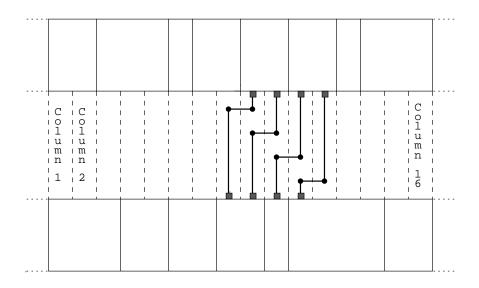

Figure 3.4: Channel with 16 columns

Channel routers can be distinguished by differences in their wiring models. One such distinction is whether a routing grid is used. Gridless channel routers constrain nets based upon the design rules. Gridded channel routers constrain nets to adhere to a *routing grid*, usually determined by the minimum size and spacing of *vias* (connections between wires in different layers). Figure 3.2 gives an example of a routing grid. The rows of the routing grid are called *rows* or *tracks* as shown in Figure 3.3. The *columns* are shown in Figure 3.4. The intersection of a row and a column yields a *gridpoint*. Gridded channel routing is easier than gridless channel routing due to the added constraint of the grid. Gridless channel routing has the advantage of being more flexible and area efficient.

Wiring models differ in the number of routing layers that can be used. Initially, channel routers used two layers. As production technology has advanced, fabrication processes with up to five layers of metal have been introduced and routers using three or more layers have been developed.

Wiring models also differ in the directions in which wires may run and the ways in which they are allowed to overlap. Overlap occurs when a wire in a higher layer is immediately above a wire in a lower layer. The directional flexibility may be physically constrained by the capabilities of the fabrication technology or artificially constrained by the layout tools in order to reduce complexity. Two common directional models are the rectilinear and octilinear models. The first allows wires to run in four directions, north, south, east, and west, and the second allows wires to run in four additional directions, northwest, northeast, southwest, and southeast.

If two or more routing layers are available, restrictions are placed on how wires in the different layers may overlap. It is useful to limit the amount of overlap in order to reduce capacitive and inductive coupling between signals in different layers. The four main overlap models are the *Manhattan*, *knock-knee*, *limited-overlap*, and *general-overlap* models.

In the Manhattan model, which is sometimes called the directional model, wire segments are restricted to running either horizontally or vertically. Additionally, each layer is restricted to carrying only horizontal or vertical segments. For instance, in a two-layer Manhattan model, the first layer might contain vertical wire segments and the second layer horizontal segments. Adjacent layers contain segments running in different directions. In three-layer channel routing, this model is further divided into the Horizontal-Vertical-Horizontal (HVH) and Vertical-Horizontal-Vertical (VHV) models. These models simply state which directions the wire segments run, with the middle layer containing either vertical (HVH) or horizontal (VHV) segments. Since this model forms a mesh-like structure, wires in adjacent layers only overlap where they cross.

The other three models do not restrict a layer to contain only vertical or horizontal segments. The only difference between the three is the amount of overlap allowed. The knock-knee model allows wires in different layers to overlap only where they cross or where they each have a corner. The limited-overlap model allows nets in different layers to overlap for short runs. The general-overlap model does not restrict the amount of overlap between nets in different layers.

An additional wiring model that has started to gain use is the *segmented* channel model [GRKG90]. Under this model, the channel has predefined segments that can be joined together, usually through programmable connections, to route signals. This model is primarily used for Field Programmable Gate Arrays (FPGAs).

#### 3.1.3 Comparing Channel Routers

Channel routing is an NP-complete problem [LP90]. As such, no channel router can generate an optimal route for all problems in a practical amount of time. Some routers will produce better routes than others when routing the same channel. There are certain characteristics of routes that are used to rate and compare routers. One characteristic is the area (height) of the generated routes. For gridded routers, sizes can be compared by the number of tracks required. For non-gridded routers the actual channel heights must be compared. Area traditionally has been the most important comparison criteria because it has a high impact on production costs.

In order to accurately judge a router's performance in terms of area, it is useful to know how close to optimal is its performance. In two-layer Manhattan routing there are two measures that provide lower bounds on the height of a channel. One reflects horizontal constraints and the other reflects vertical constraints.

The first measure, which considers horizontal constraints, is channel density. The *local* density at any point in the channel is a measure of the total height of the routing resources

Figure 3.5: Examples of density. The density at A is 0, the density at B is 2, and the density at C is 1.

required at that point. In gridded-channel routing, local density is the number of nets that start at or cross a given column. Nets that only connect terminals at the top and bottom of the same column are not included as they require no horizontal routing resources. (These nets are called trivial or single-column nets.) In non-gridded channel routing, the local density is the sum of the heights of the nets and the sum of the required spacings between the nets that start at or cross a vertical slice of the channel. The *channel density* is defined as the maximum value of all local densities within the channel.

For a density example, see Figure 3.5. The local density at A is 0, the local density at B is 2, and the local density at C is 1. Note that the density at B is 2, not 3, since one of the three nets there is a trivial net. The channel density is therefore 2, the maximum value of all local densities.

The reason that channel density provides a lower bound is that for the point in the channel where the local density, X, is equal to the channel density, X signals will have to pass through a vertical cross-section of the channel at that point. Since those X signals can not overlap because of horizontal constraints between them, there is no way that the channel could legally be routed and have a height that is less than the density at that point. Channel density reflects a lower bound arising from horizontal constraints.

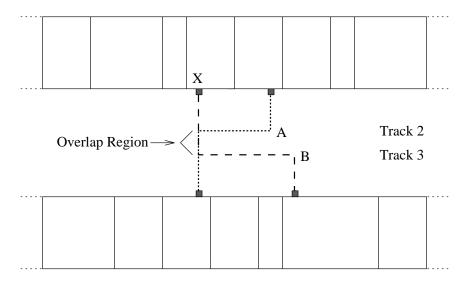

Figure 3.6: Example VCV

A lower bound reflecting vertical constraints also exists. If nets run vertically in the same layer there can be *vertical constraint violations* (VCVs). Figure 3.6 shows an example VCV. In this figure, net A has been assigned to track 2 and net B has been assigned to track 3. However, in column X net B has a connection to the top of the column and net A has a connection to the bottom of the column. If the nets were routed this way, they would be shorted together in the region between tracks 2 and 3. As such, a vertical constraint exists between nets A and B and net B must be assigned to a track that is above the track to which net A is assigned.

As all vertical constraints must be met in order to generate a valid route, the lower bound arising from these constraints can be found by generating a *vertical constraint graph* (VCG). A VCG is a directed graph in which the nodes represent nets and the edges represent vertical constraints between nets. The VCG is constructed by considering each column in which the upper and lower terminals are connected to different nets. For each such column, a node is created (if one does not already exist) for each net and a directed edge is added from the node representing the net connected to the top of the column to the node representing the net connected to the bottom of the column. Once the VCG is constructed, the number of nodes on the longest path in the graph provides a lower bound on the number of tracks that will be required for gridded routers. If any cycles exist, a route cannot be generated unless the cycles are broken. If each edge is given a weight that reflects the spacing between the center lines of the two nets it connects, the longest weighted path gives a lower bound on the channel height for gridless routers. This also requires that a source and a sink node are added to reflect the required spacing between nets and the channel edges.

Figure 3.7: Vertical constraint graph.

Figure 3.7, which shows the vertical constraint graph for Figure 3.3, presents an example of a vertical-constraint-driven lower bound. Notice that although the channel in Figure 3.3 has a channel density of two, it requires four tracks due to the channel's vertical constraints. Figure 3.3 shows that four tracks were used and Figure 3.7 shows that the vertical constraint graph has four nodes on the longest path, A-B-C-D.

Most routers are able to meet or come within a track or two of meeting these lower bounds. In cases where routers create routes of equal height, additional characteristics of the routes are used for comparison purposes. Typically total net length and total number of vias have been used. Routes that use shorter wire segments and require fewer vias are better as they are less prone to fabrication errors and less susceptible to parasitic resistances and capacitances.

#### 3.2 General Purpose Channel Routers

This section provides a sampling of two-layer Manhattan channel routers. These routers generate routes without directly considering the effects of yield, coupling, or testing, although they may try to minimize the number of vias and the length of wires. While the routers presented are by no means all that exist, they are representative of most channel routing approaches.

#### 3.2.1 Left-Edge Algorithm

Hashimoto and Stevens are credited with introducing channel routing in 1971 [HS71]. They devised channel routing as a method for routing two-layer printed circuit boards quickly and efficiently. Since its introduction the terminology has changed somewhat; for instance, what they call a *channel* is what we now call a *track* and what they call a *space* is what we now call a *channel*. The basic idea of connecting rows of parallel terminals remains the same. In order to simplify the discussion of their algorithm the terms presented earlier are used.

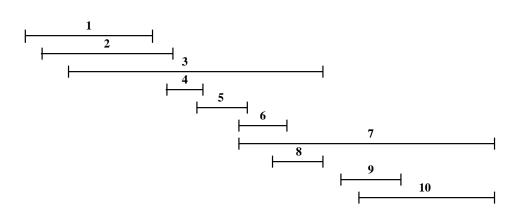

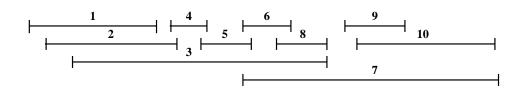

Figure 3.8: Horizontal net segments represented as intervals.

Figure 3.9: Sample net assignment.

If a net is restricted to a single horizontal segment within a channel, it can be represented as an interval with left and right bounds. If the nets are represented as such, an optimal assignment of nets to tracks can be found by performing the following steps:

- 1. Identify the leftmost-bounded, unassigned net and assign it to the current track.

- 2. Identify the leftmost-bounded, unassigned net that doesn't overlap with any nets assigned to the current track and assign it to the current track.

- 3. Repeat Step 2 until no more nets can be placed in the current track.

- 4. Add a track and return to Step 1 until all nets have been assigned.

Performing the above steps on the nets in Figure 3.8 would assign nets 1, 4, 6, and 9 to the first track, assign nets 2, 5, 8, and 10 to the second track, assign net 3 to the third track, and net 7 to the last track. The resulting assignment is shown in Figure 3.9. Because this algorithm starts at the left and always selects the left-most net, it is often referred to as the *left-edge algorithm* (LEA).

The advantage of this algorithm is that it assigns nets to a number of tracks that is equal to density. Unfortunately, it does not consider VCVs. Hashimoto and Stevens chose to resolve VCVs by rerouting one of the connections involved in each VCV as a separate stage. Because they were routing printed circuit boards, this was always possible. Another way to handle VCVs is to avoid them by not selecting a wire with unassigned ancestors in the vertical constraint graph during net selection. Enforcing vertical constraints during track assignment may generate routes that require more tracks than are necessary.

#### 3.2.2 "Greedy" Channel Router

In 1982 Rivest and Fiduccia described their greedy channel router [RF82]. They presented a column-oriented method of routing two-layer gridded channels. Their basic idea was to start at the left edge of the channel and completely wire each column before moving on to the next in order to avoid the creation of VCVs.

Their algorithm specifies that connections in a column should be made in the following order:

- 1. Bring nets with connections to the top or the bottom of the column into the channel by assigning them to the nearest track that is either empty or already contains a segment of the same net. Surprisingly, they favor a closer empty track over a further track that already contains the net. This is eventually corrected in Step 2, but is not done immediately in order to provide as much freedom as possible for the following steps.

- 2. Free as many tracks as possible by joining as many split nets, where a split net is a net assigned to multiple tracks, in the column as possible.

- 3. Add jogs to bring split net segments closer together to improve the chance of joining them later.

- 4. Add jogs to move nets closer to the channel side to which they have their next connection.

- 5. Insert a track close to the center to allow any connection that couldn't be made in the first step to be made.

- Extend the horizontal wires that continue to the next column and start again at Step 1.

As can be seen from the above, this is a heuristic algorithm that frees up as much space as possible at each step while still ensuring that all necessary connections are made. An interesting feature of this algorithm is that it can require additional routing columns on the right to join any split nets that remain. Drawbacks of this algorithm are that it generates many vias because of the jogs it adds and that it generates routes that require more tracks than later routers.

#### 3.2.3 Yoshimura and Kuh

In 1982, Yoshimura and Kuh presented two channel routing algorithms [YK82]. Both algorithms work by using the vertical constraint graph to generate routes. The general idea is to first generate a VCG and then merge nodes in the graph by considering horizontal constraints. This merging assigns nets to the same track, assuming that the nets do not overlap. In both algorithms, nodes are merged to minimize the length of the longest path in the VCG. The difference in Yoshimura and Kuh's two algorithms is that the first algorithm makes merging decisions in a "local" manner. It considers only the information represented by the current VCG when selecting between possible merges. This presents a problem since a choice may be made that prevents a better merge at a later step. Their second algorithm addresses this problem by postponing merges as long as possible. It does this by constructing a bipartite graph where the nodes on the left represent nets whose right ends have been reached and the nodes on the right represent nets whose left, but not right ends, have been reached in a left to right scan of the channel. An edge exists between a node on the left and the right if the nets represented by the nodes can coexist in the same track. At this point, any maximum matching that obeys the VCG represents the current best merging. Only when the right end of a net is reached will a node be moved from the right side of the graph to the left. When it moves, the node is merged with the corresponding node on the left if it is part of the maximum matching. When nodes in the bipartite graph are merged, the corresponding nodes in the VCG are also merged. When both algorithms complete, the merged VCG represents a valid route of the channel with each node corresponding to a track.

#### **3.2.4** Yet Another Channel Router 2

Reed, Sangiovanni-Vincentelli and Santomauro presented "Yet Another Channel Router 2" (YACR2) in 1985 [RSVS85]. YACR2 uses a modified LEA to place nets in tracks in such a manner that the number of VCVs created is minimized while the area available to fix unavoidable VCVs is maximized. Once all nets have been assigned to tracks, a series of maze routers is used to correct any VCVs that exist.

Their algorithm starts by finding a column of maximum density and assigning all the nets in that column to tracks. Next, it assigns nets to the right of the column to tracks and then nets to the left of the column to tracks. Even though YACR2 proceeds in a net by net rather than track-by-track manner, this algorithm is LEA-like in that it still optimally fills the tracks by constraining each net to a single horizontal segment and it fills each track as full as possible.

In order to increase the likelihood of generating a route, YACR2 uses an assignment procedure that considers the VCG in order to determine in which track a net should be placed. It selects the track that will leave the most flexibility for later assignments, and, if possible, it selects a track that will not generate any VCVs.

If VCV creation cannot be avoided, YACR2 tries to place the net so that the overlap, in number of tracks, of any VCVs will be kept small. By minimizing the overlap, the ability to fix the VCV should be increased. To further increase the likelihood of correcting VCVs, they avoid placing the net in the top or bottom track.

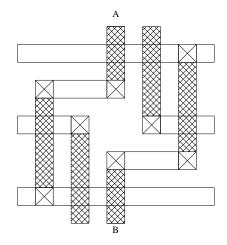

Once all nets have been assigned to tracks, vertical wire segments are added in columns without VCVs and maze routing is used to make the connections in columns with VCVs. During the maze routing stage, columns containing unresolved VCVs are considered offlimits for fixing other VCVs. The maze routing stage contains three maze routers called *maze1*, *maze2*, and *maze3*.

The first router, maze1, tries to fix the violation without adding any additional vias. In order to do this, it must violate the single direction per layer rule and use the vertical layer to make horizontal connections. Since allowing the vertical layer to run horizontally

Figure 3.10: Examples of maze1.

can cause lines to overlap for long distances, maze1 restricts any such horizontal segments to span no more than two columns. Maze1 jogs either one or both of the nets only a single column in order to resolve the VCV.

An example of a maze1 route is shown in Figure 3.10. In this figure, there is a vertical constraint between nets A and B. On the left side, the constraint has been met by jogging A to the left. On the right side, the constraint has been met by jogging both nets.

Figure 3.11: Example of maze2.

The second router, maze2, tries to resolve the remaining VCVs by adding only two vias. In order to do this, maze2 only allows one of the nets to jog, but it allows the net to jog for more than 1 column.

An example of a maze2 route is shown in Figure 3.11. In this figure, there is a vertical constraint between nets A and B. Net A has been jogged left two columns so that it can then be connected vertically to its assigned track.

Figure 3.12: Example of maze3.

The final router, maze3, tries to resolve the remaining VCVs by adding four vias. This stage allows both nets to jog for several columns. An example maze3 route is shown in Figure 3.12.

If YACR2 is unable to generate a route after trying all three maze routers, it adds a track that may allow maze2 to fix all the remaining violations. (Adding a single track doesn't help maze1. Maze3 requires the addition of two tracks.) If the channel is still unroutable, YACR2 starts over with the additional track since reassigning the nets to tracks with the additional track may generate fewer VCVs.

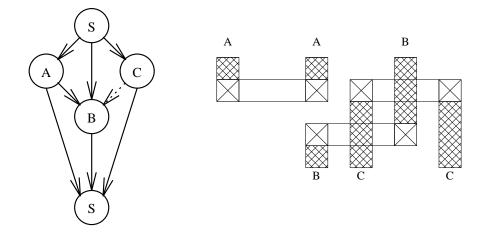

#### 3.2.5 Glitter

Chen and Kuh presented Glitter, a gridless, variable-width channel router, in 1986 [CK86]. Glitter uses an elegant, yet simple, algorithm. Chen and Kuh represented vertical, horizontal, and spacing constraints with a single graph, the *Weighted Constraint Graph* (WCG). Like previous algorithms, nets are restricted to a single horizontal segment, unless division is necessary to break vertical constraint cycles. The WCG is a superset of the VCG. Each node represents a horizontal segment and a directed edge between nodes represents a vertical constraint between the two nodes. However, there is also an undirected edge between two nodes if there is a horizontal constraint between the two nets. Each edge, directed and undirected, is given a weight representing the spacing required between the center lines of the two nets represented by the nodes. For instance, if net A has a width of 2, net B has a width of 6, and the required spacing between the two nets is 5, the weight of an edge between the two nodes representing A and B would have a weight of 9 since 2/2 + 6/2 + 5 = 9. A source and sink node representing the channel edges are also added.

Once the WCG has been constructed, Glitter generates a correct route by directing the undirected edges in the graph since this will cause all vertical and horizontal constraints to be met. To keep the channel height low, these edges are directed in a manner that minimizes the longest directed path through the graph. This implies that the undirected edges are directed in such a way that no cycles are created. Since guaranteeing a path of minimum length is itself NP-Complete, Glitter uses heuristics for directing the edges.

Figure 3.13: Undirected edge directed from C to B.

Figures 3.13 and 3.14 illustrate edge direction. In both figures, there is a directed edge (solid line) from A to B representing a vertical constraint between A and B and an

Figure 3.14: Undirected edge directed from B to C.

undirected edge (dotted line) between B and C representing a horizontal constraint between B and C. In Figure 3.13 the undirected edge between B and C has been directed from C to B. If each edge has a weight of 4, the longest path is of length 12, which represents either S-A-B-S or S-C-B-S. In Figure 3.14 the undirected edge has been directed the other way. The longest path now has length 16, from S-A-B-C-S. The case in which the edge is directed to give a shorter longest path gives better results.

One feature of this algorithm is that it can handle nets of different sizes since the weights reflect the spacing between center lines of the nets, not simply the spacing between the nets. Another feature is that it can handle irregular channel boundaries by setting the weight of an edge between the source or sink and a node to represent how far away from the respective boundary it must be.

#### 3.3 Goal Driven Channel Routers

Since a sufficient body of research exists for the basic channel routing problem of generating an area and time efficient route, channel routing research has migrated to achieving other goals. Channel routing has been used to reduce the effects of capacitive coupling, such as delay and crosstalk, to improve the yield of circuits, and to improve the testability of circuits. The work on improving testability was presented in the previous chapter. One point of interest is that while the motivation and approach may differ, much of the goal-oriented work has been accomplished by increasing the spacing between adjacent wires.

### 3.3.1 Channel Routing With Analog Considerations

The motivation for considering analog effects is to ensure that circuits function correctly and quickly. If the capacitive coupling between lines in a circuit is too large, the circuit may fail to function because of delay or crosstalk. This concern applies equally to analog circuits and high performance digital circuits.

Coupling problems are becoming worse as increases in fabrication technology lead to smaller feature sizes and faster operating speeds. Smaller feature sizes cause the lineline capacitance to dominate the line-substrate capacitance as wires come closer together [Bak90]. Additionally, as circuits begin to switch faster, the cross-talk effects rise. As a result, researchers are developing channel routing algorithms to reduce the effects of these behaviors.

In 1985 Kimble *et al.* [KDG+85] proposed a method for reducing coupling by placing standard-cells such that nets sensitive to capacitive coupling, such as analog signals, are routed in different channels than non-sensitive nets, such as digital signals. This eases the routing problem without requiring any changes in routing algorithms. This method unfortunately suffers from two drawbacks. It has a large area penalty and it does not address the problem of interaction between nets to a granularity of more than two groups. In particular, sensitive nets may still have an undesirable coupling affect upon each other.

In 1989, Gyurcsik and Jeen [Gn89] devised a method of reducing horizontal and crossover coupling capacitances. They explained how a WCG based channel router can be modified to eliminate such problems. Their method for reducing coupling capacitances between adjacent horizontal nets is to change the weight on an edge between two nodes to reflect the minimum required spacing between the nets in order to meet the capacitive coupling constraints. They show how the WCG can be modified to eliminate cross-over between two nets by forcing a vertical ordering on the edges through direction of undirected edges. To understand this, consider Figure 3.13. In this figure, B and C cross over each other once, which creates two cross-overs. The reason for this is that B and C have a common horizontal span in which B has a connection to the top of the channel, C has a connection to the bottom of the channel, and B has been assigned to a lower track than C. This means that in the WCG, the edge between B and C was directed from C to B. However, if the edge were directed the other way, the two cross-overs could be eliminated, as in Figure 3.14. Gyurcsik and Jeen noticed this and presented methods for determining when an edge could be so directed to avoid cross-overs. These methods are excellent for meeting hard-constraints, but they have a large area penalty.

In 1990, Harada, Kitazawa, and Kaneko [HKtK90] described their global and detail routing methods for reducing crosstalk by reducing the number of cross-overs that occur. Their channel router uses Gyurcsik and Jeen's method to eliminate cross-over during channel routing. As a post-processing step, it shields unavoidable crossovers by temporarily dropping the line in the lower metal layer to the poly-Si layer where it crosses under the other line. It then places a metal shielding line between them where the cross-over occurs. The weaknesses of this method are that it adds more vias, temporarily runs a line in poly, and requires that a shield line be present.

In 1990 Choudhury and Sangiovanni-Vincentelli [CSV90] eased the analog routing problem by presenting a thorough method for constraint generation. Previous work used constraints during channel routing, but did not address the constraint generation issue. In their work they show how to generate bounding and matching constraints that, given a set of performance functions and a set of parasitics, maximize the routing flexibility while still meeting performance constraints. They rate the importance of each parasitic in respect to each performance function and call these ratings *sensitivities*. They then use the sensitivity information to generate bounding constraints that meet the performance constraints while keeping the overall constraint cost low in order to maximize routing flexibility. If the constraint on a highly sensitive parasitic is increased by a small amount, the constraint on a highly insensitive parasitic can be decreased by a large amount. By keeping the overall cost of the constraint set small, any router using the constraint set should require less area to generate a route than if it were given a constraint set of higher cost. While this method provides an excellent means of weighting constraints against each other, it generates hard constraints that then must be met by the router.

In 1993 Choudhury and Sangiovanni-Vincentelli [CSV93] furthered their work by combining their techniques with both the work of Gyurcsik and Jeen and the work of Harada, Kitazawa, and Kaneko. Their work was unique in that they used shield nets to shield adjacent lines on the same layer and showed how the weighted constraint graph can be modified to do so. In addition, they also described how to modify the weighted constraint graph to keep vertical net segments that begin on opposite sides of the channel from being adjacent by adding a directed edge from the net whose vertical segment begins at the top to the net whose vertical segment begins at the bottom. Looking back at Figures 3.13 and 3.14, it can be seen that directing the undirected edge from B to C also causes the rightmost vertical segments of B and C to no longer be adjacent in addition to removing cross-overs. In 1994 Kirkpatrick and Sangiovanni-Vincentelli [KSV94] further refined this work by extending their analog sensitivity concept to include digital sensitivity.

In 1992, Mitra, Nag, Rutenbar, and Carley [MNRC92] described their global and detail mixed-signal routing system. Their system helps analog nets meet user defined Signal-to-Noise Ratios (SNRs). The channel routing part uses linear programming to budget the parasitics and then uses simulated annealing to generate a route. Simulated annealing is used to select different paths in the weighted constraint graph. The annealing cost function includes meeting of parasitic constraints as a primary objective. This method comes close to performing as a variable strength objective but closer inspection proves it to be constraint driven with an objective function for choosing between different constrained solutions.

In 1993 Chaudhary, Onozawa, and Kuh [COK93] took a different approach by fixing problems in the channel as a post-processing step. They showed how to reduce capacitive coupling by adapting compaction techniques to separate wires by adding repulsion constraints. The repulsion constraints reduce capacitive coupling between target wires by pushing them apart.

In the same year, Gao and Liu [GL93] presented a post-processing method for minimizing coupling in gridded routing solutions by reordering the routing tracks. They generated a mixed integer linear programming formulation of the track-permutation problem. They considered both vertical and horizontal adjacency in their equations and simplified the coupling problem to consider lines as coupled only if they are in immediately adjacent routing tracks. The following year they extended the work to switch-box routing [GL94]. This algorithm never causes an increase in area, but it does not allow tradeoffs to be made in area or time and it has a large time penalty.

### 3.3.2 Channel Routing for the Improvement of Yield

The motivation for considering yield during channel routing is simple. Chip manufacturers want to increase the percentage of good die on each wafer they produce. The way channel routing has been used to improve yield is to make circuits more resistant to shorts in the routing layers and resistant to opens in the vias. These problems are most often solved by increasing the spacing between wires or by reducing the number of vias.

Removing vias to improve manufacturability has been a topic since the introduction of channel routing when Hashimoto and Stevens presented an algorithm to minimize the number of vias. Since then, much work has been done. One such example is the research performed by The, Wong, and Cong [TWC89]. Their algorithm works as a post-processing step and eliminates vias by violating the directional model once a route has been generated. They try to remove vias by shifting vias and re-routing connections. Shifting a via can be thought of as sliding it in one direction and replacing the span over which it slid with the layer it drags behind it. Simple via shifting can eliminate vias if two vias bump into each other during shifting. This method can increase wire lengths, which in turn can cause additional adjacencies and increase the chance of shorts and therefore fail to meet its goal of improving yield.

In 1989, Pitaksanonkul, Thanawastien, Lursinsap, and Gandhi presented "DTR: A Defect-Tolerant Routing Algorithm" [PTLG89]. DTR reduces the probability of shorts occuring between horizontal wires by separating them through the imposition of an ordering on the tracks. This work is similar to the analog work of Gao and Liu except that it performs the separation during routing itself. DTR uses a modified version of Yoshimura and Kuh's algorithm to assign nets to tracks. It modifies the merging part to consider not only path length in the VCG, but horizontal adjacency. When two candidate merges are equal in terms of path length in the VCG, they select the one that minimizes adjacencies between tracks. They do this by making some tracks as full as possible and others as empty as possible. This way a full track and an empty track can hopefully be placed adjacent to each other later, thereby minimizing the adjacencies between the two tracks. Once all possible merges have been made, the algorithm then orders the tracks within the channel. It does this by adding undirected edges to the graph so that all node-pairs have an edge between them (the VCG is made complete). Each edge is given a weight that reflects the amount of horizontal adjacency between the wires in the two nodes it connects. At this point, a Hamiltonian path that obeys the relationships of the directed edges gives a solution that best optimizes yield by minimizing the total amount of horizontal adjacency. They use heuristics to find a minimal, or near minimal, path. Finding a path determines an ordering of tracks within the channel. Balachandran, Bhaskaran, Ganesan, and Lursinsap furthered this work in 1992 with a post-processing method for separating both horizontal and vertical wires in available space with doglegs [BBGL92], and in 1994 Tyagi, Bayoumi, and Manthravadi improved on the underlying algorithm itself [TBM94].

In 1993, Kuo introduced "YOR: A Yield-Optimizing Routing Algorithm" that reduces critical areas and vias [Kuo93]. Kuo's work is similar to the work of The, Wong, and Cong except that it focuses on reducing critical area rather than minimizing vias. YOR works as a post-processing step by performing *net floating*, *net burying*, *net burying*, and *via shifting*. Net floating and net burying involve moving a net to another layer, a higher layer

for floating and a lower layer for burying, in order to make adjacent wires run in different layers. Net bumping involves jogging a net in available space to move it further away from adjacent nets in the same layer. Via shifting is the process of partially changing the layer of a net segment by shifting the via along the segment. Since these techniques work as a post-processing step, they can be used with other algorithms. The techniques jointly consider via removal and adjacency reduction, so they don not improve one at the expense of the other.

Xue, Huijbregts, and Jess developed yield-based cost functions for a sea-of-gates router [XHJ94]. They consider extra and missing material for both single-layer and inter-layer defects and calculate an overall cost for each net segment based on its susceptibility to the above defects. They then use a Steiner tree based router to minimize the overall cost of each net based on the costs of its segments.

# 4. A Testability Enhancing Router

This chapter describes my channel router, which I will refer to as MCR, that generates more testable circuits. The underlying channel routing algorithm is an improved version [McG92] of Uzi Yoeli's robust channel routing algorithm [Yoe91], which is in turn based on YACR2[RSVS85]. MCR's basic strategy is to first place nets in tracks using a modified Left-Edge Algorithm (LEA) and then resolve VCVs with a maze router.

## 4.1 MCR

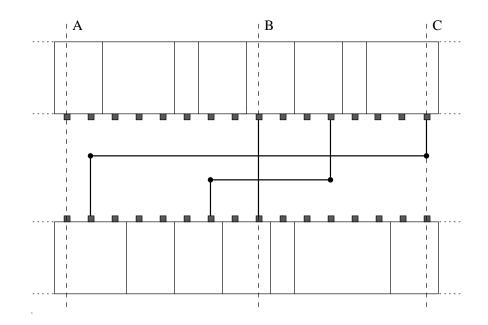

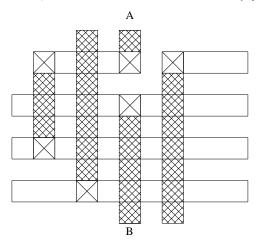

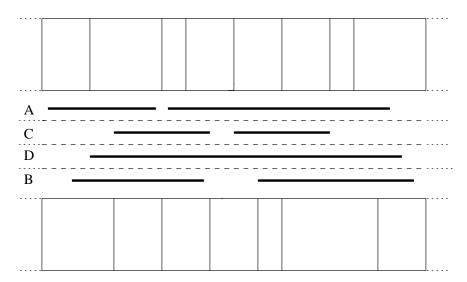

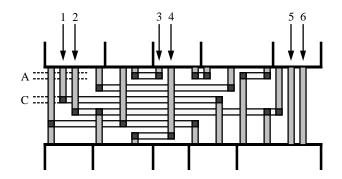

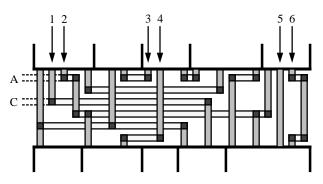

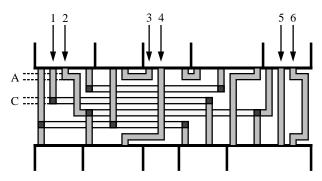

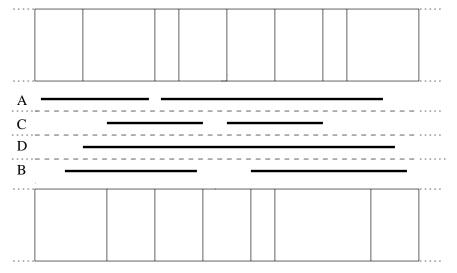

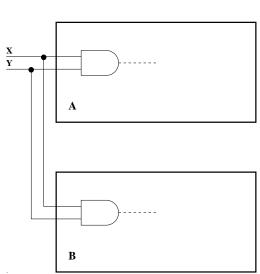

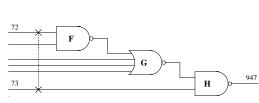

Figure 4.1: Nets are placed in tracks, alternating between the top-most and bottom-most free track. For example, first A would be filled, then B, then C, and, finally D.

In order to describe how MCR was modified to generate more testable routes, the underlying algorithm will first be described. MCR's algorithm can be assumed to be equivalent to Yoeli's algorithm except where otherwise stated.

MCR begins by filling tracks with a maximal set of non-overlapping nets. It alternates between filling the top-most and bottom-most free track. This process is illustrated in Figure 4.1. MCR starts with an initial number of tracks that is equal to the channel

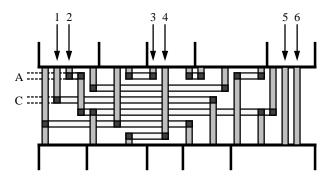

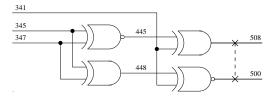

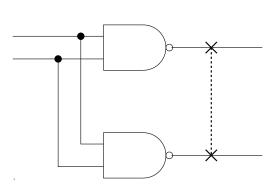

Figure 4.2: Illustration of net weights when placing nets in the topmost track. Step 1 would set the weight of A to 0 and B to 0. Step 2 would add 2 to the weight of A for the column in which A has a connection to the top and B has a connection to the bottom. Step 3 would subtract 64  $(2 \cdot 32)$  from the weight of B for the same column since placing B above A would create a VCV. Step 4 would add 120,000  $(30,000 \cdot 4)$  to both A and B for the four column span where they coexist. The final weight of A would therefore be 120,002 and the final weight of B would be 119,936.

density. When selecting nets for a given track, the desirability, which reflects the creation and resolution of VCVs, of placing each unassigned net into the given track is taken into consideration. To quantify desirability, a weighting scheme is used. Each time a net is being considered for assignment to a track, it is given a weight as follows:

- 1. Set the weight of the net equal to zero.

- 2. For each column in which the net has a connection to the channel edge that is closer and another net has a connection to the opposite edge, add the density of the column to the weight of the net.

Consider Figure 4.2, assuming that nets are being assigned to the topmost track and that the topmost track is the first track to which nets are assigned. Net A has two connections to the closest (upper) side. Since the left-most connection is in a column where A is the only net with a connection, this connection will not contribute to A's weight. The second connection to the upper edge is in a column where Net B has a connection to the lower edge. Because another net, B, has a connection to the opposite side of the channel, Net A will have the density of the column, 2, added to its weight. Since Net B only has one connection to the upper side, and that connection is in a column where no other nets have connections, its weight will not change.

3. For each column in which assigning the net to the current track will create a VCV, subtract the quantity COLUMN DENSITY · VCVWEIGHT from its weight. The subtraction is performed only if placing the net in the track under consideration will cause a VCV. If a VCV already exists in the column, the net is not penalized. VCVWEIGHT is equal to 32 by default.

Once again consider Figure 4.2, again assuming that nets are being assigned to the topmost track and that the topmost track is the first track to which nets are assigned. This step will penalize Net B's weight by  $64 (2 \cdot 32)$  since placing Net B in the topmost track would create a VCV between it and Net A. Net A will not be penalized since placing it in the top track will not cause any VCVs.

4. For each column that the net crosses in which the number of unassigned nets originating at or crossing the column is equal to the number of remaining tracks, add DENSECOL, to the weight of the net. DENSECOL is equal to 30,000 by default.

Once again consider Figure 4.2. The weights of Net A and Net B will both be increased by  $120,000 (30,000 \cdot 4)$  for the four columns in which they coexist since the number of remaining tracks is two (including the topmost track) and the number of unassigned nets for those four columns is 2. The initial number of available tracks is set to the channel density.

Before continuing, let me first discuss the purpose of the above steps. Step 1 is obviously an initialization step. The purpose of Step 2 is to encourage the early placement of a net if it can potentially create a VCV. By adding the density of the column to encourage the early placement, the congestion of the area in which the VCV would be created is taken into account. Yoeli always added to the weight of a net, regardless of whether or not another net had a connection to the opposite side. I found that by only adding to a net's weight if another net has a connection in the same column that fewer VCVs would be created to begin with and therefore fewer VCVs would need to be resolved. As a result, smaller routes can be generated [McG92].

The purpose of Step 3 is to discourage the placement of a net in a track if doing so will create a VCV. By multiplying the density of the column by VCVWEIGHT, disallowing the actual creation of a VCV, particularly one in a congested area, is given preference over the possible avoidance of a VCV, the weight added in Step 1. Where MCR's VCVWEIGHT default is 32, Yoeli set it to 8. This discrepancy arises since the designs MCR routes are larger than Yoeli's test designs. As a result, Step 2 could give a net a large enough weight that Step 3 would not have a great enough effect if VCVWEIGHT were only 8.

The purpose of Step 4 is to always ensure an assignment of nets to tracks. By adding a large enough number, at least one net in each dense column will be assigned to a track at each iteration. A dense column is a column in which the number of unassigned nets that cross or originate at the column is equal to the number of tracks that have not been assigned nets. By always assigning at least one of the nets in each dense column to a track, an assignment of nets to tracks can always be found, Yoeli proved this. The caveat here is that DENSECOL needs to be large enough to always outweigh the added bonuses or subtracted penalties of Steps 2 and 3. Since MCR is tuned for larger designs, the default value of DENSECOL was increased from 10,000 to 30,000. The value of DENSECOL needs to reflect the expected number of connections per net and the expected channel densities.

Once all nets have been given assigned weights, a optimal non-overlapping set of greatest weight is selected with a dynamic programming algorithm. The pseudocode that Yoeli gave is:

for  $(col = 1; col \le channel\_length; col = col + 1)$  {

for each net that ends at column col {

```

compute weight<sub>net</sub> + total<sub>leftcolnet-1</sub>

total<sub>col</sub> = max(total<sub>col-1</sub>, total<sub>col</sub>, weight<sub>net</sub> + total<sub>leftcolnet-1</sub>)

}

```

}

In the pseudocode, the quantity weight<sub>net</sub> is the weight of a net. The quantity  $total_{col}$  is the sum of the weight<sub>net</sub>s of the optimal set of nets that end on or before the column. The quantity  $total_{leftcol_{net}-1}$  is the  $total_{col}$  for the column that immediately precedes the leftmost column of *net*. The above code steps through the columns in the channel from left to right. For each column, it calculates the maximum total weight for any group of non-overlapping nets ending on or before the column. This quantity is termed the Maximum Accumulated Weight (MAW). When the MAW has been computed for the rightmost column, we know the maximum total weight for the set of nets that can fit in the track. The MAW is stored for each column as it is computed, so that the optimal set of nets can be retrieved at the end of the algorithm.

Before showing how to retrieve the set of nets, it is worthwhile to briefly discuss why the algorithm works. Consider what it means for the MAW to be greater at column n than it was at the previous column, n - 1. If the MAW is greater at n, there must be a net contributing to the MAW at n that does not contribute to the MAW at n - 1. Since the MAW at a column represents the maximum sum of weights of any set of nets ending on or before a column, the net contributing to the MAW at n that does not contribute to the sum at n - 1 must end at column n. Therefore to calculate the MAW at each column we need only consider the effect of nets that end at that column. If no net ends at the column, the MAW at the column is the same as that of the previous column. If a net ends at the current column, a check needs to be made to see if the weight of the net is larger the the sum of the weights of the nets that it would displace. This check can be made by calculating the effect of including the net. Since including the net will displace any nets that overlap with it, the MAW achievable by including the net must simply be the weight of the net plus the MAW of the column immediately before the leftmost end of the net. If including the net increases the MAW, the new MAW and the net that contributes to it are stored.

Once the MAW has been calculated for each column, the set of nets responsible for the final MAW can be retrieved by scanning through the columns from right to left. If at some point the MAW at column n is greater than the MAW at column n - 1, this means that a net that is part of the optimal set ends at column n. Remember, the MAW at a column can only be greater than the MAW of the previous column if a net that contributes to the higher MAW ends at the column. Since the net contributing to the increase in MAW was stored, that net can be assigned to the current track. The algorithm then skips to the column immediately preceding the left end of the net it just found and continues scanning left until the first column is reached.